CHAPTER 7

1. Pendahuluan[kembali]

2. Tujuan [kembali]

- Mempelajari dan memahami konfigurasi rangkaian aritmatika.

- Memahami cara pembuatan rangkaian aritmatika pada proteus.

- Mengetahui penggunaan rangkaian aritmatika.

3. Alat dan Bahan [kembali]

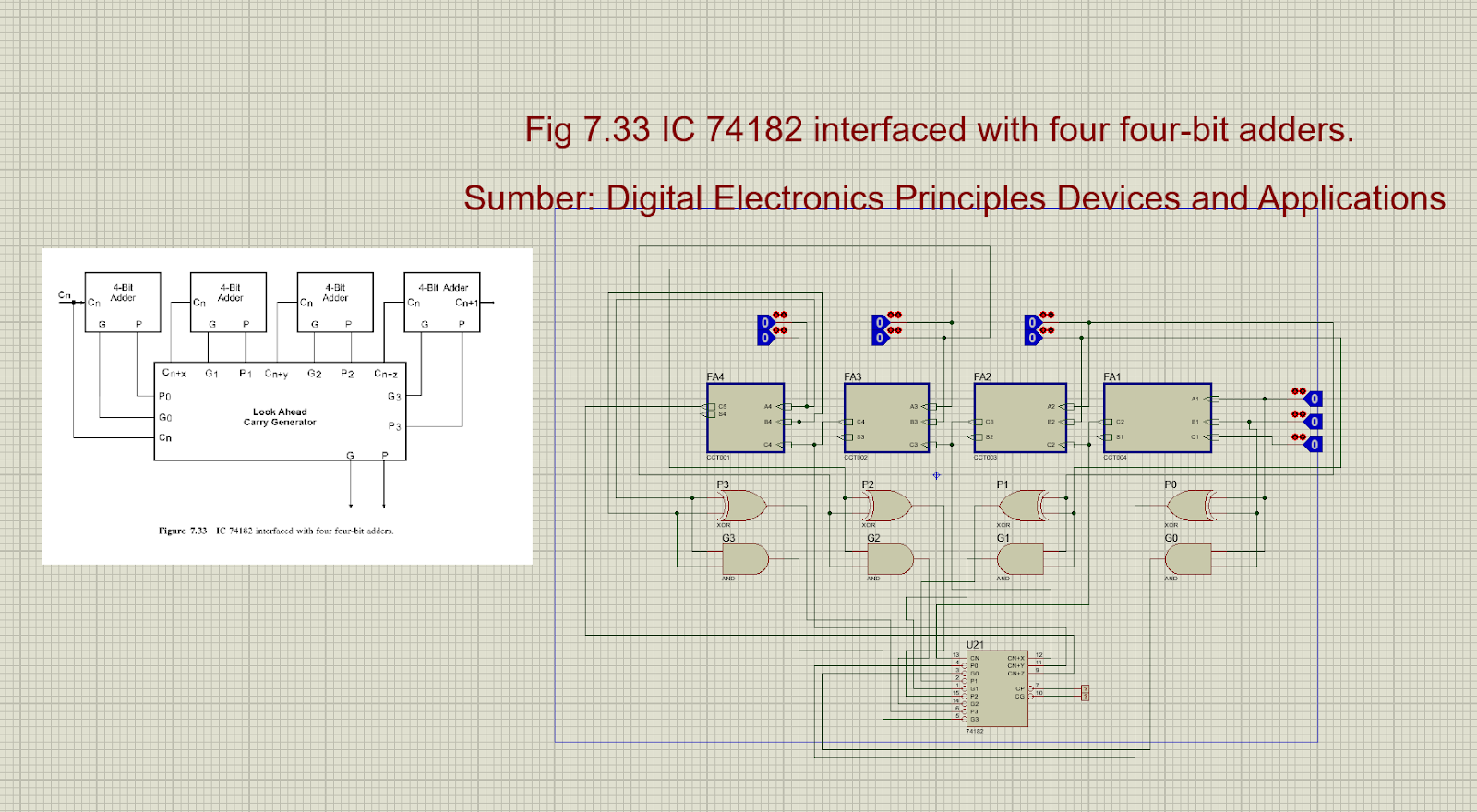

- IC 74182

IC 74182 adalah 4-bit Look-Ahead Carry Generator yang digunakan dalam rangkaian aritmetika digital, terutama dalam rangkaian penjumlah (adder). Komponen ini merupakan bagian dari keluarga TTL (Transistor-Transistor Logic) seri 74xx dan dirancang untuk mempercepat proses penjumlahan biner dengan memprediksi nilai carry (bawa) sebelum seluruh bit dijumlahkan.

IC 74182 menghasilkan carry look-ahead dari beberapa full adder 4-bit. Ini artinya, alih-alih menunggu carry dari setiap bit untuk diselesaikan secara berurutan (seperti pada ripple carry adder), IC ini menghitung semua carry secara paralel, sehingga proses lebih cepat.

- IC 74LS981

IC 74LS181 adalah 4-bit Arithmetic Logic Unit (ALU) dari keluarga TTL (Transistor-Transistor Logic) seri 74LS yang mampu melakukan berbagai operasi aritmetika dan logika pada dua bilangan biner 4-bit.

Fungsi Utama:

74LS181 digunakan untuk memproses data secara aritmetika dan logika seperti:

Penjumlahan, pengurangan

AND, OR, XOR, NOT

Operasi logika shift sederhana

Dengan kata lain, IC ini adalah jantung dari prosesor kecil zaman dulu, karena menggabungkan operasi matematika dan logika dalam satu chip.

Jenis kedua adalah gerbang OR. Sama seperti gerbang sebelumnya, gerbang ini juga memerlukan dua input untuk menghasilkan satu output. Gerbang OR ini akan menghasilkan output 1 jika semua atau salah satu input merupakan bilangan biner 1. Sedangkan output akan menghasilkan 0 jika semua inputnya adalah bilangan biner 0.

4. Dasar Teori [kembali]

Carry lookahead adder adalah rangkaian adder yang lebih cepat dalam melakukan penjumlahan biner dengan menggunakan konsep Carry Generate dan Carry Propagate. CLA disebut sebagai penerus ripple carry adder. Sirkuit CLA meminimalkan waktu tunda propagasi melalui implementasi sirkuit kompleks yang terjadi selama penambahan ini dirancang dengan mengubah rangkaian adder pembawa riak (ripple-carry adder) sedemikian rupa sehingga logika carry penambah diubah menjadi logika dua tingkat.

Dalam kasus penjumlah paralel, penambahan biner dari dua angka dimulai ketika semua bit dari augend dan tambahan harus tersedia pada saat yang sama untuk melakukan perhitungan. Dalam rangkaian penambah paralel, keluaran pembawa dari setiap tahap penambah penuh dihubungkan ke masukan pembawa dari tahap orde tinggi berikutnya, oleh karena itu disebut juga sebagai penambah tipe pembawa riak.

Dalam rangkaian penambah seperti itu, tidak mungkin untuk menghasilkan jumlah dan keluaran keluaran dari setiap tahap sampai pengangkutan masukan terjadi. Sehingga akan terjadi tunda waktu yang cukup besar pada proses penambahan , yang dikenal dengan , tunda propagasi carry. Dalam rangkaian kombinasional apa pun, sinyal harus merambat melalui gerbang sebelum jumlah keluaran yang benar tersedia di terminal keluaran.

Pertimbangkan gambar di atas, di mana jumlah S4 dihasilkan oleh penambah penuh yang sesuai segera setelah sinyal input diterapkan padanya. Tetapi input carry C4 tidak tersedia pada nilai kondisi tunak akhirnya sampai carry c3 tersedia pada nilai kondisi tunaknya. Demikian pula C3 tergantung pada C2 dan C2 pada C1. Oleh karena itu, carry harus merambat ke semua tahapan agar output S4 dan carry C5 menyelesaikan nilai kondisi tunak akhirnya.

Waktu propagasi sama dengan delay propagasi dari gerbang tipikal dikalikan dengan jumlah level gerbang di sirkuit. Misalnya, jika setiap tahap penambah penuh memiliki penundaan propagasi 20n detik, maka S4 akan mencapai nilai akhir yang benar setelah 80n (20 × 4) detik. Jika kita memperpanjang jumlah tahapan untuk menambahkan lebih banyak jumlah bit maka situasi ini menjadi jauh lebih buruk.

Jadi kecepatan jumlah bit yang ditambahkan dalam penambah paralel tergantung pada waktu propagasi carry. Namun, sinyal harus disebarkan melalui gerbang pada waktu yang cukup untuk menghasilkan keluaran yang benar atau diinginkan.

Pertimbangkan rangkaian adder penuh yang ditunjukkan di atas dengan tabel kebenaran yang sesuai. Jika kita mendefinisikan dua variabel sebagai carry generate Gi dan carry propagate Pi maka,

Jumlah keluaran dan keluaran carry dapat dinyatakan dalam bentuk carry generate Gi dan carry propagat Pi sebagai

di mana Gi menghasilkan carry ketika kedua Ai dan Bi adalah 1 terlepas dari input carry. Pi dikaitkan dengan propagasi carry dari Ci ke Ci + 1.

Fungsi carry output Boolean dari setiap tahap dalam 4 tahap carry look-ahead adder dapat dinyatakan sebagai:

Dari persamaan Boolean di atas kita dapat mengamati bahwa C4 tidak harus menunggu C3 dan C2 untuk menyebar (propagate) tetapi sebenarnya C4 disebarkan pada saat yang sama dengan C3 dan C2 . Karena ekspresi Boolean untuk setiap keluaran carry adalah jumlah produk sehingga ini dapat diimplementasikan dengan satu tingkat gerbang AND diikuti oleh gerbang OR.

Implementasi tiga fungsi Boolean untuk setiap output carry (C2 , C3 dan C4) untuk generator carry look-ahead carry ditunjukkan pada gambar di bawah.

Analisis Kompleksitas Waktu :

Kita bisa menganggap carry look-ahead adder terdiri dari dua bagian.

- Bagian yang menghitung carry untuk setiap bit.

- Bagian yang menambahkan bit input dan carry untuk setiap posisi bit.

Keuntungan dan Kerugian dari Carry Look-Ahead Adder :

- Keuntungan

- Penundaan propagasi berkurang.

- Memberikan logika penambahan tercepat.

- Kekurangan

- Sirkuit penambah Carry Look-ahead menjadi rumit karena jumlah variabel meningkat.

- Sirkuit ini lebih mahal karena melibatkan lebih banyak perangkat keras.

Soal Pilihan Ganda

Soal 1:

Apa tujuan utama dari penggunaan Look-Ahead Carry Generator dalam rangkaian penjumlah biner?

A. Untuk menghemat daya rangkaian

B. Untuk mengurangi jumlah bit hasil penjumlahan

C. Untuk mempercepat proses propagasi carry

D. Untuk menghasilkan sinyal clock eksternal

Soal 2:

Dalam rangkaian Look-Ahead Carry Generator 4-bit, sinyal Generate (G) dan Propagate (P) digunakan untuk:

A. Menyimpan data sebelumnya dan menghapus bit paling signifikan

B. Menentukan apakah carry akan dibawa ke bit berikutnya

C. Mengatur input clock dan sinyal reset

D. Menghasilkan hasil akhir penjumlahan

Soal 3:

Apa keunggulan utama dari Look-Ahead Carry Generator dibandingkan dengan Ripple Carry Adder?

A. Lebih sederhana dalam implementasi

B. Membutuhkan lebih sedikit IC

C. Mengurangi waktu delay total

D. Tidak memerlukan logika tambahan

Example

5. Percobaan [kembali]

a) Prosedur[kembali]

- Buka aplikasi proteus

- Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan gerbang XOR, Gerbang AND, dan gerbabng OR.

- Rangkai setiap komponen menjadi rangkaian yang diinginkan

- Ubah spesifikasi komponen sesuai kebutuhan

- Jalankan simulasi rangkaian.

b) Rangkaian Simulasi dan Prinsip Kerja [kembali]

c) Video Simulasi [kembali]

d) Download File [kembali]

- Download rangkaian 7.33 klik disini

- Download rangkaian 7.34 klik disini

- Download rangkaian 7.35 klik disini

- Download video 7.33 disini

- Download video 7.34 disini

- Download video 7.35 disini

- Download HTML

- Link download datasheet SN74284

- Link download datasheet SN74825

.png)

.png)

.png)

.png)

.png)

Komentar

Posting Komentar